Setting the stage

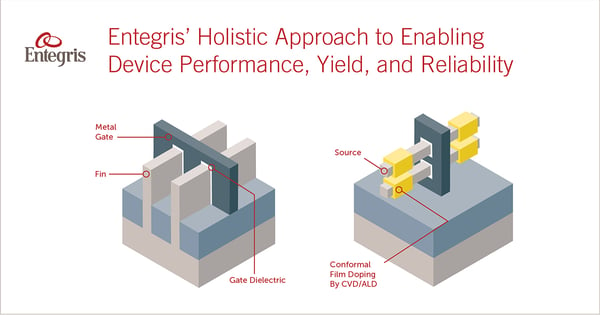

Logic devices are getting smaller, and the introduction of 3D architectures that use vertical fins and nanowires in their gate design introduce more complexity to the fabrication process. As technology nodes shrink beyond 10 nm, new materials are required in both FEOL and BEOL processes to enable performance, yield, reliability and cost.

Approaching implementation

Successful implementation of new device architectures, whether they are nanowire transistor structures or high-layer-count 3D NAND memory, can’t be accomplished merely by substituting one material with a higher-performing option. One change has a cascading effect on the entire process. Changing the interconnect metal, for example, may require new barrier films and thus new clean chemistries. And with each chemistry change, advancements in membrane technology for effective filtration are required.

Solution checklist

A complete, holistic solution should address performance, efficiency, reliability, yield, and overall cost of ownership. Whether it is new metallurgy precursors, effective delivery systems, new cleaning formulations, or new filtration membranes, find a holistic solution to your unique integration challenges.

To explore more possibilities for approaching materials processing for scaled devices, check out our recent white paper.