The Fourth Industrial Revolution is surrounding us with extraordinary technologies that did not exist a few years ago. Autonomous vehicles are already being tested on public streets. Drones range from simple adolescent playthings to short- and long-range military and civilian purposes like surveying landforms, shooting movies, and delivering packages. Vast amounts of video content, created by professionals and amateurs alike, are being filmed, streamed, and stored. Surveillance, both fixed and mobile, is becoming commonplace, server farms are bigger than ever, and 4G networks are being supplemented or replaced with 5G. What all these trends have in common is that they generate enormous amounts of data that must be processed, transported, and stored faster and more reliably than ever before.

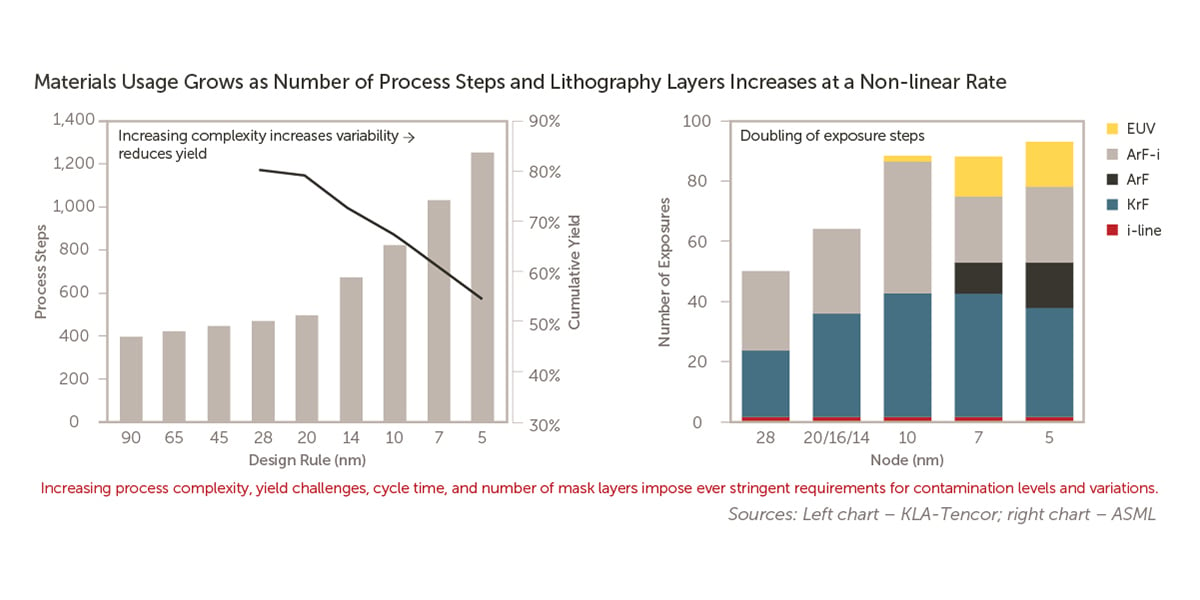

Many of these new applications require advanced logic devices to achieve greater power and processing speeds. Continued device miniaturization below the 10 nm scale, 3D architectures such as Fin field effect transistors (FinFET) and gate-all-around (GAA) transistors, and the use of new metals to reduce wiring delays and improve reliability have dramatically increased the complexity of chip manufacturing. In this environment, manufacturing yields are increasingly difficult to achieve, making the timely introduction of new logic devices more and more difficult.

The New Lithography

The continued shrinkage of logic devices brings new challenges to chip manufacturing. The ability to resolve fine patterns and place them accurately on the die is increasingly difficult at dimensions below 20 nm. Historically, the miniaturization process has been achieved through advances in optical lithography. The extent to which this miniaturization process can be extended is ultimately limited by the wavelength of the light that is used. Today’s 10 nm technology still uses light with a wavelength of 193 nm, so the size of the features on these devices is roughly 1/20 the wavelength of the light used to create them. This is a significant challenge requiring complex processing techniques, Figure 2. As features continue to shrink and today’s optical lithography pushes the physical limits imposed by the wavelength of the current ultraviolet light source, the technology has moved to even shorter wavelengths in the extreme ultraviolet (EUV) region of the spectrum.

|

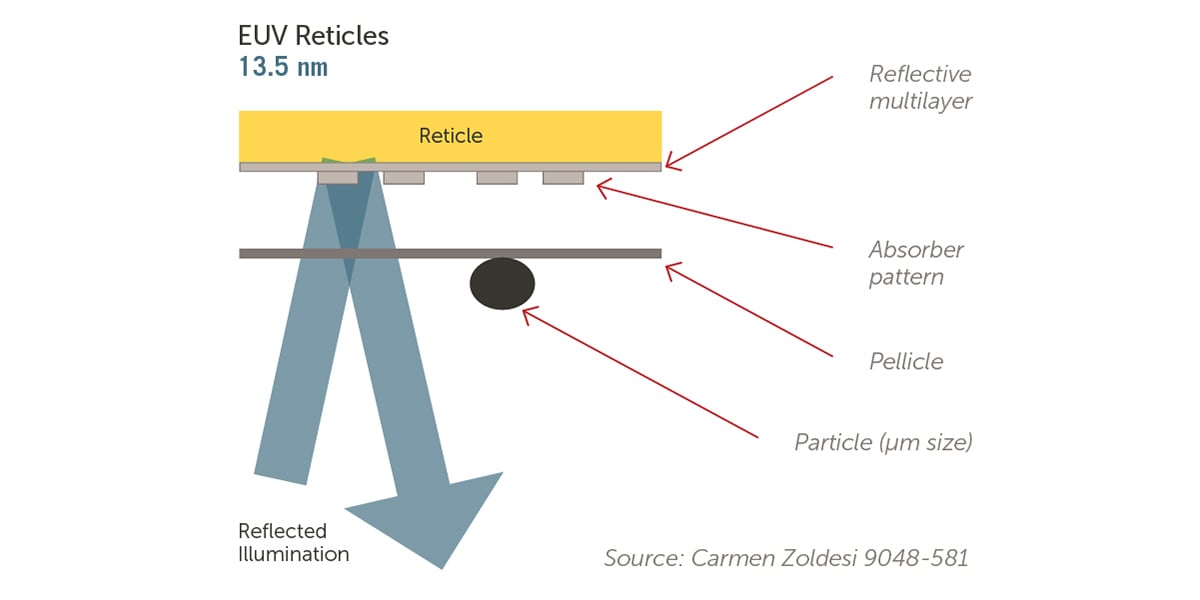

Mask Handling

Traditional optical lithography operates by passing light through photomasks consisting of fused silica and a chrome metal-absorbing film. However, masks designed to work at shorter EUV wavelengths are fundamentally different in that they are reflective and require new materials for both their substrate and pattern film. These masks are extremely sensitive to defects within or on the multilayer stack. Pellicles are typically used to protect conventional optical masks from contamination, Figure 3. Cleaning EUV reticles once they have become contaminated is a significant challenge. The solution is designing specialized protective pods specifically for handling EUV reticles.

|

Physical and Chemical Challenges

In addition to lithography challenges, fine patterns themselves are sensitive to damage by small particles and subject to structural integrity problems. Capillary effects can lead to pattern collapse during cleaning steps, and small defects and contaminants that could once be ignored can now ruin chips, either immediately or after they have been deployed. Depositing films over very small patterns with aspect ratios that can exceed 10:1 requires extremely conformal processes to achieve adequate coverage.

Materials

As chip dimensions shrink, wires that connect transistors on a chip require new metallurgies with lower resistivity to avoid signal delays and improve reliability. Engineers have been exploring materials with lower resistance such as cobalt, molybdenum, and ruthenium as replacement alternatives to copper at the smallest wiring dimensions. Precursors for these materials and the processes used to deposit these films will require further development before they are ready for high-volume manufacturing. Increasing numbers of deposition precursors are solids and the challenge of deriving a gas from the solid state requires specialized handling and delivery equipment.

Dielectrics

As transistors become smaller, the gate insulator thickness must also shrink to enable sufficient current density through the channel. For decades, silicon dioxide (SiO2) was the go-to gate oxide material. But as gate dielectrics have decreased in size, they have become “leaky” at thicknesses less than 1.2 nm. Electron tunneling allows unacceptable levels of current leakage, which increases power consumption and reduces reliability. By replacing silicon dioxide gate dielectrics with high-κ materials like hafnium (HfO2) and zirconium-based oxides (ZrO2), the insulator thickness can be increased enough to prevent electrons from tunneling through it and yet permeable enough to let the gate’s electric field penetrate the channel to turn on the transistor. These materials increase gate capacitance while controlling leakage.

Atomic Layer Processes

Small geometries with high aspect ratios (HAR) require extreme conformality to prevent being damaged by deposition of subsequent layers. Atomic layer deposition (ALD) is an effective way to achieve this degree of conformality. The process deposits a few atomic layers of a material in each of multiple cycles. This allows high levels of control and enables nearly perfect film conformality. The removal of thin films over small HAR structures often requires etch processes that can be controlled at atomic scale dimensions. These are called atomic layer etch (ALE) processes and like ALD allow fine degrees of control to lay down film layers without disturbing vulnerable underlying HAR features.

Killer Contamination

As chip features shrink the potential impact of very small contaminants grows. Particles that would not have affected yesterday’s chips can become “chip killers” today. In addition to these smaller particles, chipmakers must be concerned with dissolved ionic metal contaminants that can move through the gate oxide layer to form conduction channels and increase current leakage.

Semiconductor manufacturing will soon require purity levels measured in parts per quadrillion, so new materials must maintain near-perfect purity levels. As chip densities increase, ever-smaller particles and metal impurities in resists or in process chemicals will produce yield-sapping flaws in the resulting chips. Contaminants that previously could be disregarded because they were considered too small to affect the resulting chips now can cause problems as features shrink.

Significant advancements in filtration technology have combined porosity control in advanced polymer membranes with chemical activation of the membrane surface to selectively remove undesirable contaminants. But finer filtration alone is not the answer. As chemistry changes, there can be compatibility problems between the filters themselves and the chemicals used in chip production and cleaning.

Because chip production is a linear process, a defect or contaminant at any point in the process can affect the product. The result can be either an immediate yield reduction or a latent defect that can lead to consequential reliability failures in the field. Keeping the entire process clean with clean chemistry, compatible filter technology, and handling capability that maintains material integrity ensures maximum productivity.

Advanced Filter Technology

Historically, filters were designed to function as sieves, removing particles too large to fit through the filter’s mesh. Removing smaller particles requires a finer mesh. In today’s advanced filters, polymer membranes are engineered as multilayer films or hollow fibers to maximize the flow of liquid while retaining the greatest amount of contaminant. Chemistry can be applied to functionalize the surface of the membrane to activate the removal of specific contaminants through an absorptive process. The challenge is that unlike a sieving filter, which can be chemically inert, a chemically active surface must be compatible with all the components of a complex formulation.

Effective Wafer Handling

Smaller, more compact chips are increasingly susceptible to damage in handling or transit. As a wafer moves through the process sequence, it becomes increasingly valuable, making protecting the wafer even more important as it progresses through the build cycle.

Wafers spend most of their time in the fab within mini environments called front opening unified pods (FOUPs). While FOUPs are designed to protect the wafer from the effects of external contamination, a significant challenge comes from the wafers themselves. When wafers return to a FOUP after a given process step, they can outgas material from the chemistry to which they were exposed thereby contaminating the FOUP. To prevent contamination from outgassing, FOUP construction materials have been engineered to minimize the effect of outgassing. Gettering and purge capabilities have been added as well. Minimizing the environmental contamination is a key feature of an effective FOUP.

The Supply Chain

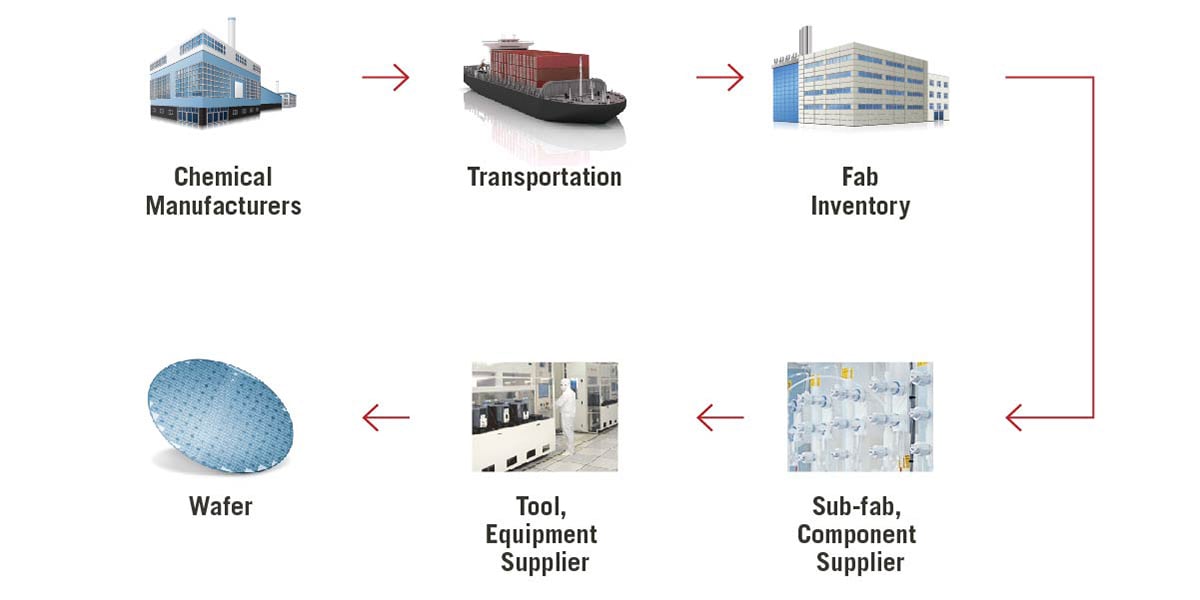

The material supply chain within the semiconductor industry is extremely complex. The path that materials follow from the point where they are manufactured to the point where they are used on the wafer may take several months and span several continents, Figure 4. The integrity of that material must be maintained from the point of manufacture to the point of use.

|

Because of the increasing challenge semiconductor manufacturers face in achieving the process yields necessary to meet timely introduction cycles of denser chips, every aspect of the fabrication process must be controlled to exacting standards as wafers move through the fab. In addition to their own processes, chip manufacturers must be concerned with con¬trolling processes further back along the supply chain to ensure that the materials and chemicals they use are clean and reliable.

Additionally, while new materials can bring significant benefits to device or process performance, an understanding of the interactions of these materials with each other or with components in the process is essential. When new materials and equipment are individually sourced, responsibility for avoiding problems falls on the chipmaker’s process engineers. Working with suppliers that address multiple aspects of the process may offer more comprehensive insight into the wafer life cycle, which can be used to enhance the fab’s in-house expertise and problem-solving speed.

Summary

New applications are emerging that require faster, more powerful processors, and denser memory chips. Faster devices have long meant smaller devices, and today, performance gains are being extended with new materials and new transistor architectures. The physics of these devices demands thinner insulating dielectrics, new metallurgies for interconnect wiring, high-k gate dielectrics, and high-mobility channel materials.

Chipmaking is a “cascading” process. Each of the inputs — materials or process — flows directly into the finished chips, interacting with other materials and processes along the way. To ensure efficiency and yield in the chip manufacturing process, it is critical to consider not only the purity of the material inputs, but also the integrity of those materials along their journey to the wafer. Enabling advanced chip technology will require precision, purity, and attention to detail, but the payoff will be leadership in the most profitable segment of a growing market.

Read the full paper here: Examining Chip Manufacturing Challenges for Advanced Logic Architecture. For more solutions visit the Entegris’ website.